Altera Intel Agilex 5 FPGAは、Intel 7テクノロジーを採用して構築されており、Intel®の第2世代Hyperflex™ FPGAアーキテクチャ、最大28.1Gbpsまでサポートする高速トランシーバ、PCIe 4.0 x8、最大4000MbpsのDDR5に対応したインターフェイス、1.05V~3.3Vの汎用I/Oなど、高度な機能を備えています。そのため、有線/無線通信、映像/放送機器、産業アプリケーション、試験/測定製品、医療用電子機器、データセンター、防衛アプリケーションなど、エッジからコアまでをカバーするミッドレンジFPGAアプリケーションに最適です。

特徴

- 高度なIntel技術とプロセスを使用して製造

- 第2世代Intel Hyperflex FPGAアーキテクチャによって大幅な設計最適化が可能になり、Cyclone V FPGAに比べて最大2.5倍高い性能または最大50%低い総電力を実現

- データ集約型アプリケーションを対象とした最大32 x 28Gbpsデータレート、および強化されたメディアアクセス制御、物理的コーディングサブレイヤ(PCS)、ネットワークアプリケーションを対象とした最大16 x 25Gbpsイーサネット(GbE)の順方向エラー訂正(FEC)をサポート

- 強化されたPCI Express (PCIe)サポート、最大PCIe 4.0 x8インターフェイス

- 業界標準DDR4、DDR5、LPDDR4、LPDDR5をサポート

- 2コアのCortex-A55(最大1.5GHz)および2コアのCortex-A76(最大1.8GHz)を搭載したマルチコアArm®プロセッサ

- Cyclone V FPGAに比べてINT8動作で最大37X1ピーク理論トップの改善が備わったAI Tensorブロック

- 1レーンあたり最大3.54GbpsでのMIPI D-PHY v2.5

アプリケーション

- 産業用:

- スマートファクトリーのAI、エッジAI

- スマートファクトリーオートメーション

- センサ/モータ/ドライブ/接続、機能安全性、セキュリティ

- I/OモジュールとIoTデバイス

- 小型PLCとエッジAI

- 医療:

- 診断用画像および映像

- 患者モニタリング

- 監視システム、小売、コンスーマ:

- スマートシティ/小売、V2X

- トラック、バスシステム、列車と鉄道、EV充電表示処理

- 接続性とビデオ処理

- IP経由のビデオ

- 家庭用電子機器(AR/VR、ドローン、ゲーム)

仕様

- Dシリーズ:性能と電力効率のために最適化されており、さまざまな市場における多くのアプリケーションに最適

- 103K ~ 644K LEs

- 最小23mm x 23mmのパッケージサイズ

- 最大32x 28Gトランシーバ

- 最大PCIe 4.0 x8および25GbE x16ハードIP

- DDR4 @ 3,200Mbps、DDR5 @ 4,000Mbps、LPDDR4/4x/5 @ 4.267Mbps、QDR IV @ 2.132Mbps

- 最大56ピークトップINT8

- 最大3680の18x19乗算器

- 1.5GHzでのデュアルコアA55および1.8GHzでのデュアルコアA76のマルチコアArmプロセッサ

- 1レーンあたり最大3.5GbpsでのMIPI D-PHY v2.5

- Eシリーズ-電力とサイズ向けに最適化されており、エッジ、組み込み、その他でのインテリジェントアプリケーションに最適

- 50K ~ 656K LEs

- 最小15mm x 15mmのパッケージサイズ

- 最大24x 28Gトランシーバ

- 最大PCIe 4.0 x4および10/25GbE x6ハードIP

- 2.667MbpsでDDR4、3,600MbpsでDDR5、3.733MbpsでLPDDR4/5

- 最大26ピークトップINT8

- 最大1692の18x19乗算器

- 1.5GHzでのデュアルコアA55および1.8GHzでのデュアルコアA76のマルチコアArmプロセッサ

- 1レーンあたり最大3.5GbpsでのMIPI D-PHY v2.5

ビデオ

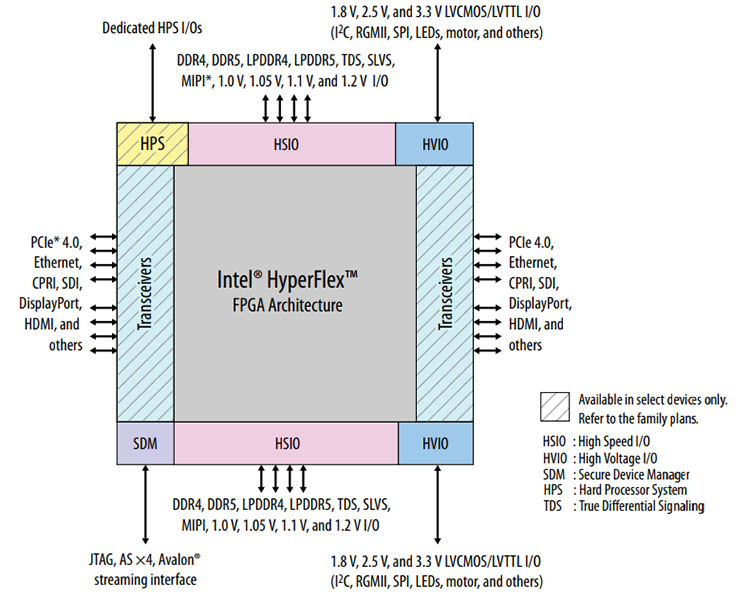

ブロック図

インフォグラフィック

公開: 2024-03-25

| 更新済み: 2026-01-21