Lattice Semiconductor MachXO4™フィールドプログラマブルゲートアレイ

Lattice Semiconductor MachXO4™ フィールドプログラマブルゲートアレイ (FPGA) は、Lattice Semiconductorの超低密度FPGAポートフォリオを拡充した製品で、柔軟性と効率性をもたらす高度機能を提供します。MachXO4デバイスは、低電力消費、内蔵フラッシュメモリ、高I/O密度、インスタントオン(瞬時起動)機能を兼ね備え、最先端のシステムニーズを満たします。MachXO4は、小型パッケージにもかかわらず極めて高いI/O密度を実現しているだけでなく、システムのコストとフットプリントの最小化に貢献する強化された機能も内蔵しています。さらに、幅広いプログラマビリティおよび業界標準インターフェイスへのネイティブサポートを備えたこれらのFPGAは、進化するコネクティビティおよび制御アプリケーション向けのスケーラブルなソリューションです。Lattice Radiant™ソフトウェアを使用すると、生産性の高い設計を強化できます。本ソフトウェアは、業界をリードするRTL合成、統合された設計データベース、高度スクリプト機能、最先端のGUI、タイミング解析、組み込みロジックアナライザを備え、大規模な設計や複雑な設計をサポートしています。Latticeは、MachXO4™ファミリ向けに事前設計されたIPモジュールも幅広く提供しています。

特徴

- バリエーション(すべて機能互換およびピン互換)

- ZC - 超低消費電力、2.5V/3.3V電源

- HC - 高性能、2.5V/3.3V電源

- HE - 高性能、1.2V電源

- 不揮発性メモリ混載の65nm低消費電力プロセス用に構築

- 静的電力が最低で140µWという超低消費電力

- 896 LUT~9400 LUTの幅広いロジック密度の選択範囲

- 最大448KBのユーザーフラッシュメモリ (UFM) を備えた内蔵フラッシュメモリ

- 最大432KBの内蔵ブロックメモリ (EBR) 、54KBの分散型RAM

- 高速ブート時間5ms以内のインスタントオン起動

- 従来デバイスと次世代デバイスの接続用に3.3V、1V I/O規格をサポートする柔軟性が高いバッファ

- 最低リーク電流350µAの低ホットソケット機能、電源シーケンスなし

- LVCMOSおよびLVTTL I/Oタイプの混合電圧をサポート

- デフォルトでプルダウン抵抗を内蔵しており、外付け部品の削減が可能

- 最大382x個のI/Oピンを備え、I/O対LUT比が高いコンパクトなパッケージ

- SPI、I2C、タイマー/カウンター、発振器をチップに内蔵し機能強化を実現

- Lattice Radiantソフトウェアを使用した設計生産性の向上

- RoHS準拠

アプリケーション

- 計算

- データセンターサーバ

- ネットワーキングとストレージ

- ハードウェアアクセラレーション

- 通信機器

- イーサネットスイッチおよびルータ

- ブロードバンドアクセス

- 無線ユニット

- 家電製品

- ディスプレイモニター

- カメラ

- スマートフォン

- 産業/電力

- モータ制御

- ハンドヘルドデバイス

- 試験および計測

- プログラマブルロジックコントローラ

- 自動車向け(末尾が A の部品)

- ADAS

- インバータ

- モータ制御

- インフォテインメント

- バッテリ管理

仕様

- 低消費電力およびプログラマブルアーキテクチャ

- ロジック密度範囲 896~9.4k LUT4

- 内蔵ブロックメモリ (EBR) 64KB~432KB

- 分散型RAM 最大54KB

- 専用のFIFO制御ロジック

- 高度な65nm低消費電力プロセス

- プログラム可能な低振幅差動I/O

- スタンバイモードおよびその他の省電力オプション

- 高性能で柔軟なI/Oバッファ

- プログラム可能なsysIO™バッファは各種インターフェイスに対応

- LVCMOS 3.3/2.5/1.8/1.5/1.2/1.0

- LVTTL

- LVDS、Bus-LVDS、MLVDS、LVPECL

- MIPI D-PHYエミュレーション

- シュミットトリガ入力、最大0.5Vヒステリシス

- I/Oはホットソケットに対応

- オンチップ差動終端

- プルアップまたはプルダウンモードを設定可能

- プログラム可能なsysIO™バッファは各種インターフェイスに対応

- 事前設計されたソース同期I/O

- I/OセルでのDDRレジスタ

- 専用のギアリングロジック

- ディスプレイI/O用の7:1ギアリング

- 汎用DDR、DDRx2、DDRx4

- さまざまな高度パッケージ

- 最大382個のI/Oピン、高I/O対LUT比の小型パッケージ

- 0.4mmピッチ - 1280~4320 LUT、超小型フットプリントのWLCSP (2.5mm × 2.5mm~3.8mm × 3.8mm)、27~62個のI/O

- 0.5mmピッチ - 896~4320 LUT、8mm x 8mm BGA~20mm x 20mm TQFPパッケージ、最大112個のI/O

- 0.8mmピッチ - 1280~9400 LUT、14mm x 14mm~19mm x 19mm BGAパッケージ最大382個のI/O

- 1.0mmピッチ - 1280~4320 LUT、17mm x 17mm BGAパッケージ、204個のI/O

- 不揮発性で複数回の再構成が可能

- インスタントオン - ミリ秒以内の起動

- オプションで外部SPIメモリを使用したデュアルブート

- 1チップの安全なソリューション

- JTAG、SPI、またはI2Cでプログラム可能

- 商用/産業用デバイス向け最大100,000回、車載デバイス向け10,000回の書き込み/消去サイクルが可能な再構成可能フラッシュメモリ

- バックグラウンドでプログラム可能な不揮発性メモリをサポート

- TransFR再構成を使用したシステム状態をI/Oが保持しつつ、現場でのロジック更新が可能

- 最適化が可能なオンチップクロッキング

- 商用/産業用デバイス向け精度5.5%のオンチップ発振器

- 8つのプライマリクロック

- 高速I/Oインターフェイス用の最大2個のエッジクロック(上側と下側のみ)

- 分数分周方式(Fractional-N)の周波数シンセサイザを備えた、デバイスあたり最大2つのアナログPLL

- 広い入力周波数範囲 7MHz~400MHz

- 強化されたシステムレベルのサポート

- オンチップ実装のハード化機能 ― SPI、I²C、およびタイマ/カウンタ

- システム追跡用の固有トレースID

- 拡張された動作範囲を持つ単一電源

- IEEE標準 1149.1バウンダリスキャン

- IEEE 1532準拠のインシステムプログラミング

- 最先端の設計ソフトウェア

- Lattice RadiantはMachXO4デバイスをサポート

- VHDL、VHDL-2008、Verilog、SystemVerilogのRTL言語を業界最高水準でサポート

- コマンドライン上での高度なスクリプト機能、およびTCL設計フロー

- 1クリックのコンパイルフロー、および解析ツール間でのクロスプローブ(相互参照)

- 組み込みタイミングおよびロジックアナライザ

PFU ブロック図

MachXO4デバイスのコアはPFUブロックで構成されており、ロジック、算術、分散型RAM、分散型ROM機能を実行するようにプログラムできます。各PFUブロックは、0~3の番号が付けられた4つの相互接続されたスライスで構成されています。各スライスには、2つのLUTと2つのレジスタが含まれています。各PFUブロックには、53個の入力と25個の出力が紐付けられています。

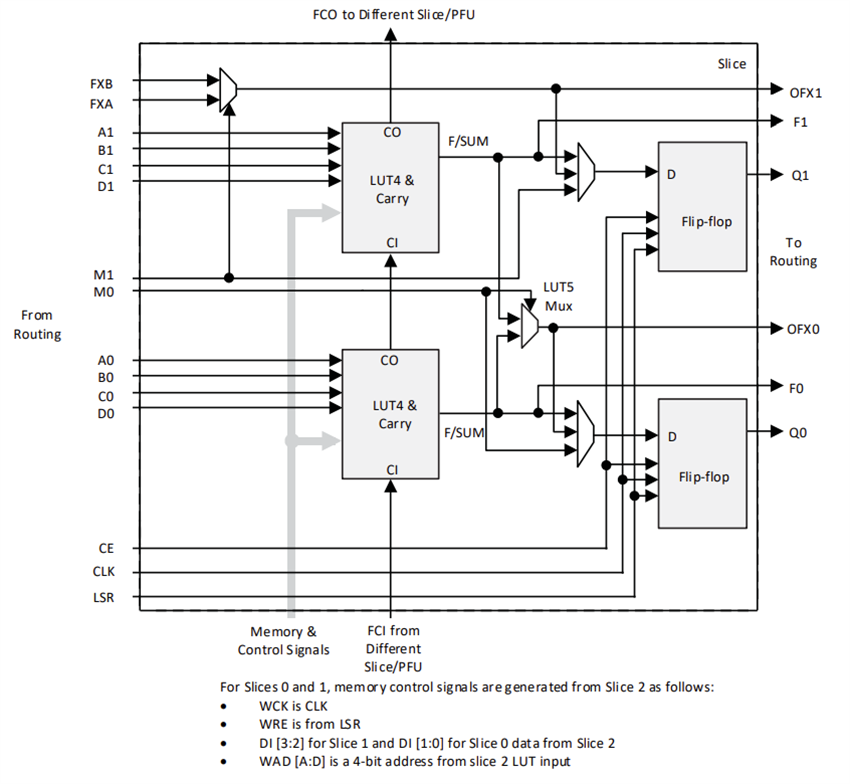

スライス図

スライス0~3には、2つのレジスタに供給する2つのLUT4が含まれています。スライス0~2は、分散型メモリとして構成できます。制御ロジックは、セット/リセット機能(同期式/非同期式としてプログラム可能)、クロック選択、チップ選択、より広範なRAM/ROM機能を実行します。スライス内のレジスタは、ポジティブ/ネガティブエッジトリガ、またはレベル応答クロックとして構成できます。すべてのスライスは、ルーティングから15個の入力と、キャリーチェーン(隣接するスライスまたはPFUから)から1個の入力を持ちます。ルーティング用6個、(隣接するPFUへの)チェーン接続用1個、の合計7個の出力があります。

PLL 図

MachXO4 PLLは、ユーザーロジックから動的に変更される分周値などのPLL設定が可能になるWISHBONEポート機能を搭載しています。この機能を使用する場合は、WISHBONEポートへのアクセスを可能にするために、EFBブロックも設計時にインスタンス化する必要があります。動的な位相調整と同様に、PLLの設定がWISHBONEポート経由で更新されると、PLLはロックを失い、tLOCKパラメータが満たされるまで再ロックしない可能性があります。