Microchip Technology ZL3026x miClockSynthユニバーサルクロックジェネレータ

Microchip ZL3026x miClockSynthユニバーサルクロックジェネレータは、複数のクロック周波数を複数の負荷に分配することで、設計の信頼性を向上させ、BOMコストを削減し、設計を簡素化します。ZL3026xデバイスは、ボード上の複数の乗算器、シンセサイザ、オシレータに取って代わる複雑なクロックツリーを作成します。小型パッケージとクラス最高のジッタ性能を備えたこのデバイスは、厳しいジッタ予算と厳しいボードスペース制限のあるクロック合成および周波数変換アプリケーションを対象としています。特徴

- 柔軟な入力クロック 4個

- 水晶/CMOS入力 1個

- 差動/CMOS入力 2個

- シングルエンド/CMOS入力 1個

- 9.72MHz~1.25GHzの任意の入力周波数(CMOSの場合は最大300MHz)

- アクティビティモニタ、自動/手動スイッチング

- ピンまたはレジスタによるグリッチレスクロックスイッチング

- 外部または内部EEPROMからの電源投入時の自動自己構成、最大8個の構成をピン選択可能

- ゼロ遅延アプリケーション用の外部フィードバック

- 数値制御発振器モード

- スペクトラム拡散変調モード

- PCIe 1、2、3、4準拠のクロックを生成

- 外部VCXOまたはループフィルタ部品を必要とせずに簡単に構成できる設計

- SPIまたはI2Cプロセッサ・インターフェイス

- コア電源電圧オプション

- 2.5Vのみ

- 3.3Vのみ

- 1.8V+2.5V

- 1.8V+3.3V

- 省スペース8mm2 QFN-56(0.5mmピッチ)

- 6種類または10種類の任意の周波数、任意のフォーマット出力

- 1Hz~1045MHzの任意の出力周波数

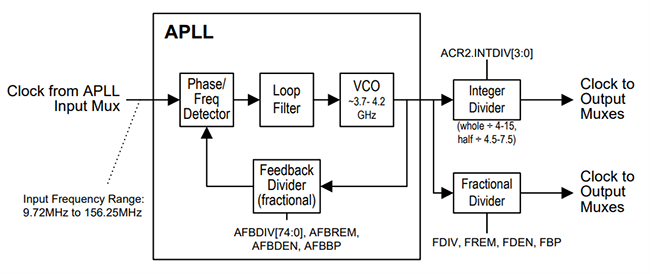

- 誤差0ppmの高解像度frac-N APLL(ZL30260~ZL30263)

- APLLには分数分周器と整数分周器があり、2つの独立した周波数ファミリ(ZL30260-ZL30263)を作成します。

- 誤差0ppmのフラクショナルN APLL(ZL30264-ZL30267)2個

- 各APLLには分数分周器と整数分周器があり、合計4つの独立した周波数ファミリ(ZL30264-ZL30267)を作成

- 出力ジッタ

- 最低0.17ps RMS(12kHz~20MHz)の整数乗算と分周器から

- 分数分周器からは、通常1ps RMS未満、多くの周波数は0.5ps RMS未満

- 各出力には独立した分周器あり

- 各出力は、LVDS、LVPECL、HCSL、2xCMOS、またはHSTLとして構成可能

- 2xCMOSモードでは、PピンおよびNピンを異なる周波数(例:125MHzと25MHz)に設定可能

- 1.5V~3.3VのCMOS出力電圧を備えた複数の出力電源電圧バンク

- 正確な出力アライメント回路と出力ごとの位相調整

- 出力ごとの有効化/無効化およびグリッチレススタート/ストップ(ストップハイまたはストップロー)

アプリケーション

- 放送ビデオ

- 産業用イーサネットネットワーキング

- データセンター

- インフォテインメント

- ヒューマン・マシン・インターフェイス(HMI)

仕様

- 電源電圧

- 高コア範囲:2.375V~3.465V

- 低コア範囲:1.71V~1.89V

- 非クロックI/Oピン範囲:1.71V~2.625V

- OCx出力範囲:1.425V~2.625V

- 水晶発振周波数範囲:25MHz~60MHz

- 最大シャントキャパシタンス:5pF(標準2pF)

- 負荷容量範囲:8pF~16pF(標準10pF)

- 等価直列抵抗(ESR)範囲:50Ω~60Ω

- 最大水晶駆動レベル:100µW、200µW、300µW(標準)

- 非クロックCMOSピン

- 入力/出力リーク電流:±10µA

- 最大入力容量:10pF(標準3pF)

- 最大入力ヒステリシス:11pF(標準3pF)

- GPIOピンでのクロック出力

- 周波数:50MHz

- 標準立ち上がり/立ち下がり時間範囲:1.2ns~2.3ns

- XAクロック入力負荷サイクル範囲:40%~60%

- クロック入力

- 入力差動電圧範囲:0.1V~1.4V

- 1.35VDC 標準入力バイアス電圧、内部バイアス)

- 入力周波数

- 差動範囲:9.72MHz~1250MHz

- シングルエンド範囲:9.72MHz~300MHz

- 標準入力抵抗:50kΩまたは80kΩ

- LVDSクロック出力

- 最大周波数:1045MHz

- コモンモード電圧範囲:1.13V~1.37V

- 差動電圧範囲:310mV~530mV

- 標準立ち上がり/立ち下がり時間範囲:150ps

- 負荷サイクル範囲:45%~55%

- LVPECLクロック出力

- 最大周波数:1045MHz

- コモンモード電圧範囲:

- VDDOx = 2.5Vの場合、1.13V~1.33V

- VDDOx = 3.5Vの場合、1.85V~2.05V

- 差動電圧範囲:650mV~1050mV

- 標準立ち上がり/立ち下がり時間範囲:150ps

- 負荷サイクル範囲:45%~55%

- HCSLクロック出力

- 最大周波数:250MHz

- コモンモード電圧範囲:0.6V~0.95V

- 標準立ち上がり/立ち下がり時間範囲:250ps

- 負荷サイクル範囲:45%~55%

- CMOSおよびHSTL(クラスI)クロック出力

- 最高周波数範囲:1Hz~250MHz

- 標準立ち上がり/立ち下がり時間範囲:0.4ns~2.2ns

- 負荷サイクル範囲:42%~58%

- 出力無効時の標準電流:300µA

- APLL周波数

- VCO範囲:3715MHz~4180MHz

- PFD入力範囲:9.72MHz~156.25MHz

- ジッタとスキュー

- 標準APLLジッタ転送帯域幅:600kHz

- 最大出力対出力スキュー:100ps

- 動作温度範囲:-40°C~+85°C

APLLのブロック図

その他の資料

公開: 2023-08-18

| 更新済み: 2023-08-22