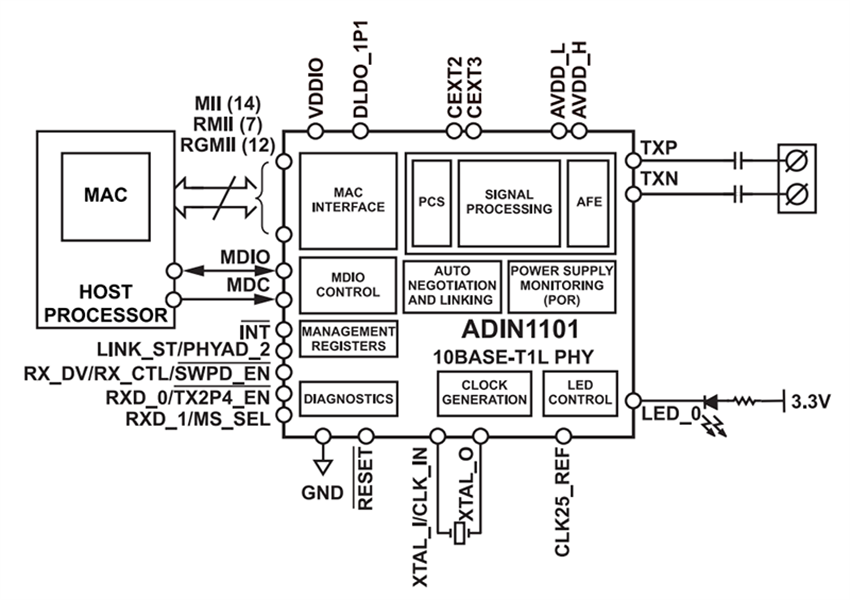

Analog Devices Inc. ADIN1101低電力10BASE-T1L PHYトランシーバ

アナログ・デバイセズ (Analog Devices) 低消費電力 10BASE-T1L PHYトランシーバは、産業用イーサネットアプリケーション向けに設計されたシングルポートデバイスで、長距離用の10Mbpsシングルペアイーサネット(SPE)を対象としたIEEE® 802.3cg-2019™ イーサネット規格に準拠しています。ADIN1101には、イーサネット物理層(PHY)コアが統合されており、関連するすべてのアナログ回路、入力/出力クロックバッファ、管理インターフェイス制御レジスタ、サブシステムレジスタ、ならびにMACインターフェイスと制御ロジックが搭載されており、リセット、クロック制御、ピン構成を管理できます。ADIN1101は、オートネゴシエーション機能を有効にした状態で最大1700メートルのケーブル接続距離をサポートし、消費電力はわずか39mWという超低消費電力です。PHYコアは、IEEE 802.3cg規格で指定されている1.0Vp-pおよび2.4Vp-pの両方の動作モードをサポートしています。1.8Vまたは3.3Vのいずれかの単電源で実行でき、1.0Vp-p送信レベルを可能にする1.8Vオプションがあります。システムの信頼性を向上させるために、ADIN1101には、内蔵電圧監視およびパワーオンリセット(POR)回路が搭載されています。

ホストプロセッサまたはMACとAnalog Devices ADIN1101の間の通信は、2線式 MDIOインターフェイス経由で処理され、PHYコアの制御レジスタとステータスレジスタへのアクセスを実現しています。このインターフェイスは、IEEE 802.3規格の第22節および第45節の両方との互換性があります。

特徴

- 10BASE-T1L IEEE規格802.3cg-2019準拠

- ケーブルは1.0Vp-pおよび2.4Vp-pで最大1700mまで到達します

- 1.0Vp-pおよび2.4Vp-p送信レベルをサポート

- MDI極性検出と訂正

- 45mWの低消費電力

- 診断

- TDRを用いたケーブル障害検出

- フレームジェネレータとチェッカー

- MSEを用いたリンク品質インジケータ

- フレームジェネレータとチェッカー

- 複数のループバックモード

- IEEEテストモード対応

- MII、RMII、RGMII MACインターフェイス

- MDIO管理インターフェイス

- ピンストラップを使用した非管理構成

- 2ピンMDI

- 内部終端レジスタとハイブリッド

- 25MHzクリスタルまたは外部クロック入力(RMII向け50MHz)

- 単電源または二電源供給動作:1.8Vまたは3.3V

- 3.3V、2.5V、または1.8V MACインターフェイスVDDIO供給

- 統合電源監視とPOR

- EMCのテスト基準

- IEC 61000-4-4 EFT (±4kV)

- IEC 61000-4-2 ESD (±4kV接触放電)

- IEC 61000-4-2 ESD(±8kV気中放電)

- IEC 61000-4-5サージ (±4kV)

- IEC 61000-4-6伝導耐性(10V/m)

- IEC 61000-4-3放射耐性(クラスA)

- EN 55032放射妨害波(クラスB)

- 小型32リード、5mm × 5mm LFCSPパッケージ

- 温度範囲

- 工業用:-40°C~+85°C

- 拡張温度範囲:-40°C +105°C

アプリケーション

- プロセス制御

- ファクトリーオートメーション

- ビルオートメーション

- 現場計器とスイッチ

仕様

- 4mA ~ 8mA出力駆動電流範囲

- クロック

- 外部水晶(クリスタル)

- 周波数: 25MHz 標準

- 周波数公差: ±30ppm

- <>

- 60Ω最大等価直列抵抗(ESR)

- 1.5pF標準入力容量

- 18pF最大負荷容量、標準10pF

- 最大起動時間 2ms

- クロック入力(CLK _ IN)

- 25MHzまたは50MHz標準入力周波数

- 入力電圧範囲0.8Vp-p~2.5Vp-p

- 入力負荷サイクル: 45% ~ 55%

- 6kΩ標準駆動ポイント抵抗

- 3pF標準駆動ポイント容量

- 40ps最大ジッタ公差(RMS)

- CLK25_REF クロック出力

- 周波数: 25MHz 標準

- 45% ~ 55%負荷サイクル

- 40ps (最大)長期ジッタ公差(RMS)

- 外部水晶(クリスタル)

- タイミングとレイテンシ

- <>

- 標準レシーバレイテンシ: < 3.2μs="">

- 標準5μs未満の総レイテンシ

- パワーアップタイミング

- 40ms最大電源ランプ時間

- 内部パワーグッド範囲に対する20ms ~ 43ms最小時間間隔

- 6µs~14µsのハードウェア構成ラッチ時間

- 50ms最大管理インターフェイスアクティブ

- 電力要件

- 1.71V~3.46Vの幅広い電源電圧範囲

- 1.0Vp-p送信レベル(単電源)

- 25mA標準電源電流

- 100%データスループットで45mWの消費電力、フルアクティビティ;ソフトウェアパワーダウンモードで11mW

- 2.4Vp-p送信レベル(単電源)

- 33mA標準電源電流

- 100%データスループットで109mW消費電力、フルアクティビティ;ソフトウェアパワーダウンモードで22mW

- 2.4Vp-p送信レベル(デュアル供給)

- 電源電流範囲: 15mA ~ 16.5mA (標準)

- 100%データスループットで81mW消費電力、フルアクティビティ;ソフトウェアパワーダウンモードで11mW

- 管理インターフェイスのタイミング

- 400ns最小MDC期間

- 100ns最小MDC高時間

- 100ns最小MDC低時間

- 5ns最大MDC立ち上がり/立ち下がり時間

- MDCまでの10ns最小MDIO信号セットアップ時間

- MDCに対する10ns最小MDIO信号保持時間

- MDCに対する300ns最大MDIO遅延時間

機能ブロック図

公開: 2025-09-10

| 更新済み: 2025-09-16