Texas Instruments AM263Px/AM263Px-Q1 ARM®ベースMCU

Texas Instruments AM263Px/AM263Px-Q1 ARM®ベース・マイクロコントローラ(MCU)は、次世代の産業用および自動車組み込み製品の複雑なリアルタイム処理ニーズを満たすように設計されています。AM263Px/AM263Px-Q1 MCUファミリは、最大4つの400MHz ARM Cortex®-R5Fコアを備えた複数のピン・ツー・ピン互換性デバイスで構成されています。ARM R5Fサブシステムは、オプションとして、複数の機能安全構成用にロックステップまたはデュアルコアモードで実行するようにプログラムできます。産業用通信サブシステム (PRU-ICSS) は、Ethernet/IP® 、EtherCAT® 、PROFINET® (その他多数) 、標準イーサネット接続、カスタムI/Oインターフェイスなどの産業用イーサネット通信プロトコルの統合を可能にします。このファミリは、高度なデジタル・アクチュエーションとアナログ・センシング・モジュールにより、将来のデジタル・パワーおよびモーター制御アプリケーション向けに設計されています。複数のR5Fコアは、256KBの共有緊密結合メモリ(TCM)と3MBの共有SRAMを備えたクラスタ・サブシステムに配置され、外部メモリの必要性が大幅に減少します。オンチップのメモリ、ペリフェラル、相互接続の信頼性を高めるため、拡張ECCが搭載されています。ハードウェア・セキュリティ・マネージャ(HSM)は、きめ細かいファイアウォールを管理し、開発者がセキュリティを重視した厳格なシステム設計要件を実装できるようにします。セキュアブートと暗号化加速度は、AM263Pxデバイスでも利用可能です。Texas Instruments AM263Px-Q1デバイスは、自動車アプリケーション向けのAEC-Q100認定を受けています。

特徴

- プロセッサコア

- 各コアが最大400MHzで動作するシングル、デュアル、クアッドコアのArm Cortex-R5F MCU。

- CPUコアあたり64ビットECC付き16KB Iキャッシュ

- CPUコアあたり32ビットECC付き16KB Dキャッシュ

- CPUコアあたりx256統合VIM

- CPUコアクラスタあたり32ビットECC付き256KB緊密結合メモリ(TCM)

- ロックステップまたはデュアルコア対応クラスタ

- 三角関数を高速化する三角関数演算ユニット (TMU)

- 最大4x、R5F MCUコアあたり1つ

- 各コアが最大400MHzで動作するシングル、デュアル、クアッドコアのArm Cortex-R5F MCU。

- メモリ

- OptiFlashメモリ テクノロジーとeXecute In Place (XIP) サポートを備えたフラッシュ・サブシステム1つ

- 1つのオクタル・シリアルペリフェラルインターフェイス(OSPI)、最大133MHzのSDRおよびDDR

- AM263Pフラッシュ・イン・パッケージ (ZCZ_F) バリアントには8MB OSPI フラッシュが含まれています

- OptiFlashメモリ テクノロジーとeXecute In Place (XIP) サポートを備えたフラッシュ・サブシステム1つ

- 3MBのオンチップRAM(OCSRAM)

- 6バンク x 512KB

- ECCエラー保護

- 内部DMAエンジンのサポート

- 外部メモリ用のリモートL2キャッシュ、CPUコアあたり最大128KB、ソフトウェアでプログラム可能

- システムオンチップ(SoC)サービスとアーキテクチャ

- データ移動機能をサポートする1x EDMA

- 2つのトランスファー・コントローラ (TPTC)

- 1つのチャンネル・コントローラ (TPCC)

- デバイスのブートは、以下のインターフェイスからサポートされます:

- UART(プライマリ/バックアップ)

- QSPI NORフラッシュ(4S/1S)(プライマリ)

- OSPI NOR フラッシュ (8S 50MHz SDR Mode0、8S 25MHz DDR XSPI) (プライマリ)

- プロセッサ間通信モジュール

- 複数のコアで実行されるプロセスを同期するためのSPINLOCKモジュール

- CTRLMMRレジスタを通じて実装されるMAILBOX機能性

- 時間同期および比較イベント割り込みルーターによる中央プラットフォーム時間同期(CPTS)のサポート

- タイマ モジュール

- 4つのウィンドウ付きWatchdogタイマ(WWDT)

- 8つのリアルタイム割り込み(RTI)タイマ

- データ移動機能をサポートする1x EDMA

- 接続全般

- 6つのユニバーサル非同期RX-TX(UART)

- 8つのシリアルペリフェラルインターフェイス(SPI)コントローラ

- 5x ローカル相互接続ネットワーク (LIN) ポート

- 4x 集積回路間 (I2C) ポート

- CAN-FDをサポートする8つのモジュラ・コントローラ・エリア・ネットワーク(MCAN)モジュール

- 4つの高速シリアルインターフェイス・トランスミッタ(FSITX)

- 4つの高速シリアルインターフェイス・レシーバ(FSIRX)

- 最大139個の汎用I/O(GPIO)ピン

- センシングと作動

- リアルタイム制御サブシステム (CONTROLS)

- 柔軟な入力/出力クロスバー(XBAR)

- 5つの12ビット アナログ/デジタル・コンバータ(ADC)

- 最大4MSPSの6入力SAR ADC

- 6つのシングルエンド・チャンネル OR

- 3つの差動チャンネル

- 最大4MSPSの6入力SAR ADC

- 高度に構成可能なADCデジタル論理

- XBAR 変換開始トリガー(SoC)

- ユーザー定義サンプル・アンド・ホールド(S+H)

- 柔軟な後処理ブロック(PPB)

- 1つのレゾルバ・サブシステム(ZCZ-SおよびZCZ-Fパッケージ)と

- 2つの レゾルバ‐デジタルコンバータ (RDC) OR

- 2つの12ビットADCは汎用にも使用可能

- 最大3MSPSの4入力SAR ADC

- 4つのシングルエンド・チャンネル OR

- 2つの差動チャンネル

- 最大3MSPSの4入力SAR ADC

- Type-Aプログラム可能なDACリファレンス(CMPSSA)付き10つのアナログコンパレータ

- Type-Bプログラム可能なDACリファレンス(CMPSSB)付き10つのアナログコンパレータ

- 1つの12ビット・デジタル/アナログ コンバータ(DAC)

- 32x パルス幅変調(EPWM)モジュール

- シングル/デュアルのPWMチャンネル

- 高度なPWM構成

- 拡張HRPWM時間分解能

- 16つの拡張キャプチャ(ECAP)モジュール

- 3つの拡張直交エンコーダ・パルス(EQEP)モジュール

- 2つの4チャンネル シグマ‐デルタ・フィルタ・モジュール(SDFM)

- 追加の信号多重クロスバー(XBAR)

- 産業用接続

- プログラム可能なリアルタイムユニット - 産業用通信サブシステム(PRU-ICSS)

- デュアルコア・プログラム可能なリアルタイム・ユニット・サブシステム(PRU0 / PRU1)

- 決定論的ハードウェア

- 動的FirmWare

- デュアルコア・プログラム可能なリアルタイム・ユニット・サブシステム(PRU0 / PRU1)

- PRUあたり20チャンネルの拡張入力(eGPI)

- PRUあたり20チャンネルの拡張出力(eGPO)

- 組み込みペリフェラルおよびメモリ

- UART×1、ECAP×1、MDIO×1、IEP×1

- 1つの32KB共有汎用RAM

- 2つの8KB共有データRAM

- PRUあたり1つの16KB IRAM

- ScratchPad(SPAD)、MAC/CRC

- デジタルエンコーダとシグマ‐デルタ制御ループ

- PRU-ICSSは、以下のような高度な産業用プロトコルを可能にします:

- EtherCAT、Ethernet/IP™、

- PROFINET、IO-Link注文用

- 専用の割り込みコントローラ(INTC)

- 動的CONTROLSS XBAR統合

- プログラム可能なリアルタイムユニット - 産業用通信サブシステム(PRU-ICSS)

- 高速インターフェース

- 最大2つの外部ポートをサポートする統合3ポートのギガビットイーサネット・スイッチ(CPSW)

- MII(10/100)、RMII(10/100)、またはRGMII(10/100/1000)

- IEEE 1588(2008附属書D、附属書E、附属書F)(802.1AS PTP搭載)

- 第45条MDIO PHY管理

- 512x ALEエンジンベースのパケット分類器

- 最大2KBのパケットサイズによるプライオリティ・フロー制御

- 4つのCPUハードウェア割り込みペーシング

- ハードウェアでのIP/UDP/TCPチェックサムオフロード

- 最大2つの外部ポートをサポートする統合3ポートのギガビットイーサネット・スイッチ(CPSW)

- セキュリティ

- Auto SHE 1.1/EVITAをサポートしているハードウェア・セキュリティ・モジュール(HSM)

- ARM Cortex-M4Fベースの専用セキュリティ・コントローラ

- タイマ、WWDT、RTC、割り込みコントローラなどの絶縁された安全なRAMsPeripherals

- CRC、ESM、PBISTなどの安全関連ペリフェラル

- セキュアブートサポート

- デバイスのテイクオーバー保護

- ハードウェアによるルート オブ トラスト(RoT)

- 2組のRoTキーをサポート

- 認証ブートのサポート

- 暗号化ブートのサポート

- SW アンチロールバック保護

- デバッグ・セキュリティ

- 暗号化認証後にのみ安全なデバイスのデバッグ

- 永久デバッグ/JTAGディセーブルのサポート

- デバイスIDとキー管理

- ユニークID(SoC ID)

- OTPメモリ(FUSEROM)のサポート

- 広範なファイアウォールのサポート

- 様々なインターフェイスに存在するシステム・メモリ保護ユニット(MPU)

- 暗号化加速度

- DMAサポート付き暗号化コア

- AES - 128/192/256ビットのキーサイズ

- SHA2 - 256/384/512ビットをサポート

- 擬似および真の乱数発生器(TRNG)による決定論的乱数ビット発生器(DRBG)

- RSA/Elliptic曲線暗号化(ECC) 処理を支援する公開キーアクセラレータ (PKA)

- Auto SHE 1.1/EVITAをサポートしているハードウェア・セキュリティ・モジュール(HSM)

- 機能安全

- 機能安全要件があるシステムの設計が可能

- SAFETY_ERRORn ピンが指定されたエラー信号化モジュール(ESM)

- 計算が重要なメモリのECCまたはパリティ

- 4つのデュアル・クロック・コンパレータ(DCC)

- 3つの自己テスト・コントローラ(STC)

- CPUとオンチップRAM用のプログラム可能な組み込み自己テスト(PBIST)とフォールト注入

- 電圧、温度、クロックの監視、ウィンドウ付きwatchdogタイマ、メモリ整合性チェック用CRCエンジンを含むランタイム内部診断モジュール

- 機能安全性準拠の対象[産業用]

- 機能安全アプリケーション用に開発済

- IEC 61508機能安全システム設計を支援するために利用可能な文書

- SIL-3までの体系的対応能力に対応

- SIL-3ターゲットのハードウェア整合性

- 安全関連認定

- IEC 61508予定

- 機能安全性準拠の対象[自動車]

- 機能安全アプリケーション用に開発済

- ISO 26262機能安全システム設計を支援するために利用可能な文書

- ASIL Dターゲットの体系的な機能

- ASIL-Dターゲットのハードウェア整合性

- 安全関連認定

- ISO 26262計画中

- 機能安全要件があるシステムの設計が可能

- データストレージ

- 1つの4ビット マルチメディア・カード/セキュア・デジタル (MMC/SD) インターフェイス

- 最適な電源管理ソリューション

- TPS653860-Q1電源管理IC(PMIC)が推奨されます

- Companion PMICは、デバイスの電源要件を満たすために特別に設計

- さまざまな使用事例をサポートするためのフレキシブルなマッピングと工場出荷時にプログラムされた構成

- TPS653860-Q1電源管理IC(PMIC)が推奨されます

- テクノロジー/ パッケージ

- 自動車アプリケーション向けのAEC-Q100認定済み

- 45nm技術

- ZCZパッケージ

- AM263x 互換性(ZCZ-C)

- AM263xとのピン・ツー・ピン互換性オプション

- AM263Px レゾルバ(ZCZ-S)

- 新しいリゾルバ・サブシステム機能性の追加

- フラッシュインパッケージのAM263Px レゾルバ(ZCZ-F)

- 内部接続されたシリコン イン パッケージ (SIP) 64Mb ISSI IS25LX064-LWLA3 OSPI フラッシュ・デバイスが 1 つ含まれます。最大133MHzのSDR および DDR

- AM263x 互換性(ZCZ-C)

- 324ピンNFBGA 15.0mm x 15.0mm x 0.8mmピッチ

アプリケーション

- ACインバータとVFドライブ

- バッテリマネジメントシステム

- コンボボックスアーキテクチャ

- DC/DCコンバータ

- ドメインコントローラ

- EV充電

- IOアグリゲータ

- オンボードチャージャー

- 再生可能エネルギー貯蔵

- 単軸および多軸サーボドライブ

- ソーラーエネルギー

- テレマティクス

- トラクション・インバータ

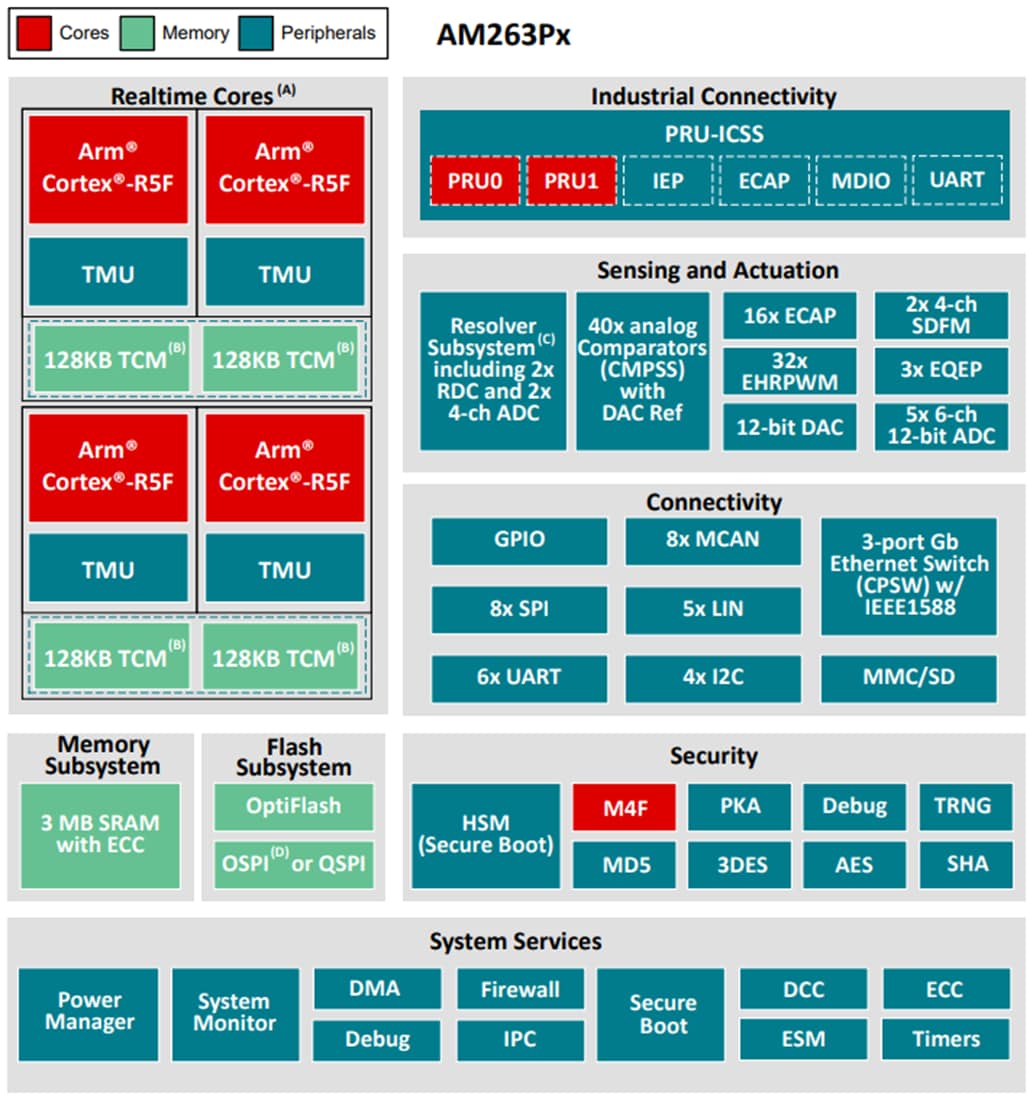

機能ブロック図

公開: 2024-06-26

| 更新済み: 2025-06-06